안녕하세요. "기억하고자 하는 모든 것"을 담아내는 "리멤버미" 입니다.

오늘은 NMOS와 PMOS의 신호 전달 특성에 대해 알아보겠습니다.

NMOS의 경우 아래 그림과 같이 0V는 잘 전달하지만 Vdd는 Vth 만큼 깎여서 전달하게 됩니다.

Gate에 Vdd가 걸려서 NMOS가 on 되었다고 하면 Vgs는 Vdd-0V 이며 값이 변하지 않게됩니다.

그러므로 Vout이 0V에 도달할때까지 전류는 흐르게 됩니다.

반면에 Vin에 Vdd를 걸어주게 되면 Source 는 Vout이 됩니다.

이때 Vgs는 Vdd-Vout 전압으로 Vin에 의해 Vout이 Vdd에 가까워 질수록 Vgs는 0에 가까워집니다.

하지만 Vgs는 NMOS의 Vth 전압 이상이되야 on되기 때문에

Vout이 Vdd-Vth값에 도달하게되면 NMOS는 off되게 되며 더이상 전류는 흐리지 않고

Vout은 Vdd-Vth로 holding 되게 되죠.

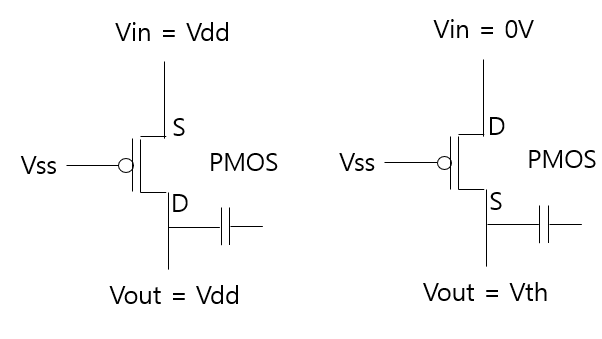

그렇다면 PMOS는 어떨까요?

아래 그림과 같이 VDD는 잘 전달하지만 0V는 Vth만큼 높은전압으로 전달하게 됩니다.

Vin이 Vdd라면 source는 VDD가 되게 되고 Vgs는 Vss-Vdd로 고정이 됩니다.

그러면 PMOS는 계속 ON되어있고 Vout은 Vdd까지 도달하게 됩니다.

반면 0V를 걸게되면 source는 Vout이 되며 Vgs는 Vss-Vout이 됩니다.

결국 Vout이 0V에 가까워지면서 Vth에 도달할대 PMOS는 off되게 되며

Vout은 Vth값으로 holding되게 됩니다.

NMOS와 PMOS 설계 시 위에 전달 특성을 잘 이해하셔야 합니다.

궁금하신 내용있으면 댓글 달아주세요~! ^^

'기억하고 싶은 지식 > 반도체' 카테고리의 다른 글

| [전자/반도체/회로]Static 과 Dynamic 회로의 명확한 구분! 면접 질문! (0) | 2023.02.07 |

|---|---|

| [전자/반도체]NMOS와 PMOS의 Drain과 Source 위치가 가끔 헷갈리다면?! 꿀팁! (0) | 2023.02.07 |

댓글