안녕하세요.

“기억하고자 하는 모든 것”을 담아내는 리멤버미입니다.

MOSFET이나 CMOS 회로를 보다 보면 문턱전압 Vth를 하나의 고정된 값처럼 다루는 경우가 많습니다.

그런데 실제 회로에서는 Vth가 항상 그대로 있지 않습니다. 특히 source와 body(또는 bulk, substrate) 사이에 전압이 생기면, 문턱전압 자체가 달라집니다. 이 현상을 바로 바디 효과(Body Effect) 또는 substrate bias effect라고 부릅니다.

이번 글은 좀 이해하기 어려울 수 있습니다. 먼저 핵심부터 짚고 차근차근 풀어가겠습니다.

2026.04.09 - [기억하고 싶은 지식/반도체] - [전자/반도체]문턱전압(Vth)이란 무엇인가: 트랜지스터가 켜지는 진짜 기준

[전자/반도체]문턱전압(Vth)이란 무엇인가: 트랜지스터가 켜지는 진짜 기준

안녕하세요.“기억하고자 하는 모든 것”을 담아내는 리멤버미입니다. 반도체나 디스플레이, 회로 이야기를 보다 보면 문턱전압(Vth, Threshold Voltage) 이라는 말을 정말 자주 보게 됩니다.MOSFET 설

diary.remembermeeternally.com

먼저 결론부터

NMOS 기준으로 보면, source가 body보다 더 높은 전위에 있을수록, 즉 VSB가 커질수록 문턱전압 Vth는 증가합니다.

다시 말해 같은 gate 전압을 걸어도 예전보다 채널이 덜 잘 만들어지고, 결과적으로 transistor가 더 늦게 켜지는 것처럼 보입니다. U of Toronto와 UC Davis 강의 자료도 모두 source-body 전압이 커질수록 threshold voltage가 증가한다고 설명합니다.

조금 더 회로적으로 말하면, transistor의 실제 구동 여유인 VGS − Vth가 줄어드는 것입니다.

그래서 drain current가 감소하고, source follower에서는 출력 스윙이 줄어들고, 직렬로 쌓인 MOS 구조에서는 위쪽 소자의 구동력이 약해지는 문제가 나타납니다.

바디 효과는 왜 생길까

이 현상을 이해하려면 MOSFET이 사실 3단자가 아니라 4단자 소자라는 점을 먼저 떠올리면 좋습니다.

우리가 보통 gate, drain, source만 생각하지만 실제로는 body 단자가 하나 더 있고, 이 body 전위가 채널 형성 조건에 영향을 줍니다. U of Toronto 자료도 MOSFET을 본질적으로 4-terminal device로 설명합니다.

NMOS를 예로 들면, source-body 사이에 전압이 생기면 source-body 접합은 보통 더 강한 reverse bias 상태가 됩니다. 그러면 채널 아래의 depletion region이 더 넓어지고, gate가 반전층을 만들기 위해 감당해야 할 전하 조건이 더 커집니다.

결국 gate 입장에서는 “예전과 같은 채널을 만들기 위해 더 높은 전압이 필요해진다”는 뜻이고, 그 결과가 바로 Vth 증가입니다. UC Davis 강의노트는 threshold voltage의 구성 요소에 depletion charge 항이 들어가며, VSB가 0이 아닐 때 threshold가 달라진다고 정리합니다.

즉, 바디 효과를 한 문장으로 줄이면 이렇습니다.

body 전압이 바뀌면 채널을 만들기 위한 조건이 바뀌고, 그 결과 문턱전압도 함께 움직인다.

식으로 보면 어떻게 바뀔까

NMOS에서 가장 널리 쓰이는 바디 효과 식은 다음과 같습니다.

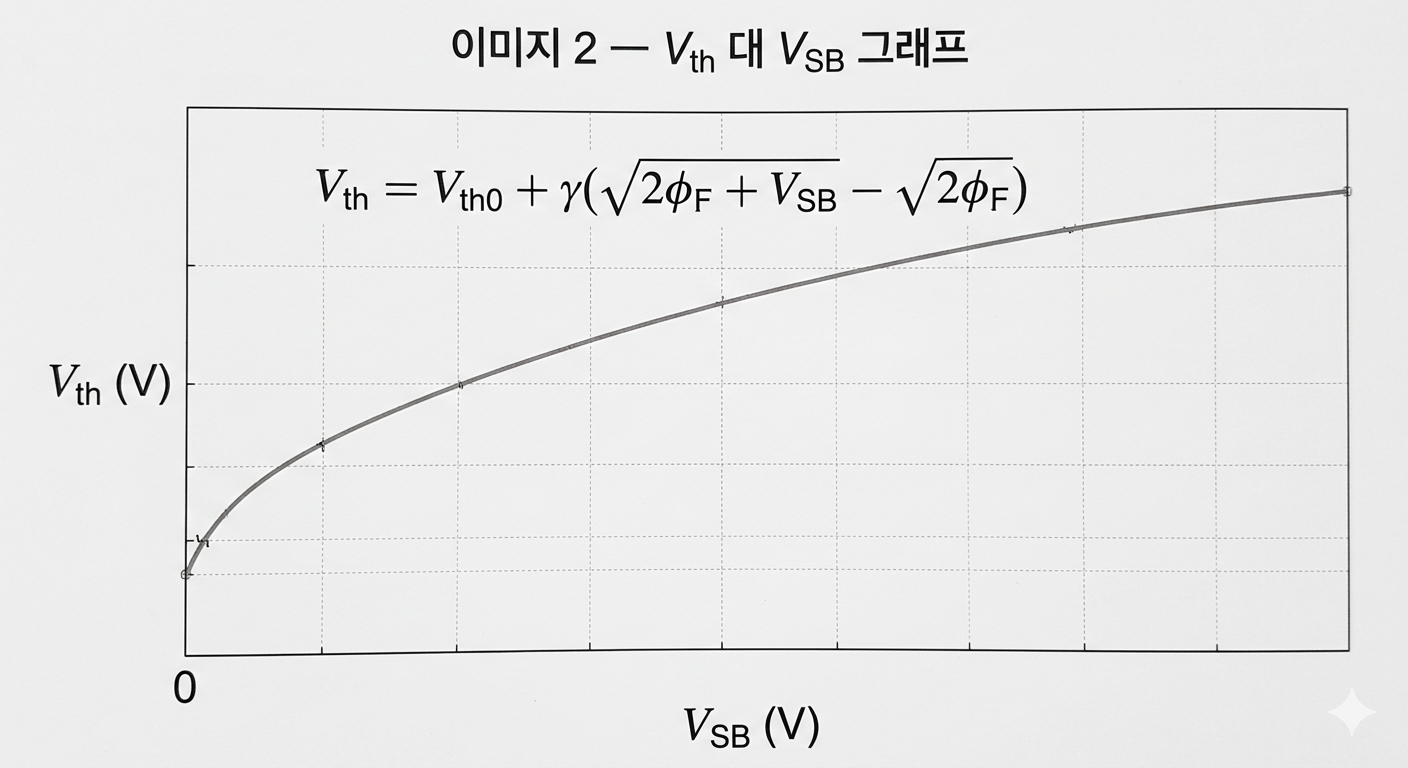

Vth = Vth0 + γ(√(2φF + VSB) − √(2φF))

여기서 각 항의 의미는 다음과 같습니다.

- Vth0 : VSB = 0일 때의 문턱전압

- γ : body effect coefficient

- φF : Fermi potential 관련 항

- VSB : source-body voltage

U of Toronto 강의 자료는 이 식을 그대로 제시하면서, VSB가 증가하면 Vt가 증가한다고 설명합니다. 같은 자료는 2φF를 예시적으로 약 0.6V 수준으로 두고 설명하며, γ는 공정과 산화막 조건에 따라 달라지는 계수라고 정리합니다.

여기서 중요한 포인트는 단순히 “비례해서 증가한다”가 아니라 제곱근 형태로 증가한다는 점입니다.

즉, VSB가 커질수록 Vth는 계속 올라가지만, 증가량은 완전히 직선적이지 않습니다. 처음에는 민감하게 올라가다가 점점 완만해지는 형태를 생각하면 이해가 쉽습니다. 이 제곱근 형태 역시 강의 자료의 식 자체에서 바로 확인할 수 있습니다.

결국 전류에는 어떤 영향을 줄까

Vth가 올라가면 가장 직접적으로 바뀌는 것은 overdrive voltage, 즉 VGS − Vth입니다.

예를 들어 gate에 1.2V를 걸고 있었고 원래 문턱전압이 0.5V였다면, overdrive는 0.7V입니다.

그런데 body effect 때문에 Vth가 0.7V로 올라가면 overdrive는 0.5V로 줄어듭니다.

이 차이는 생각보다 큽니다.

MOSFET 전류는 강반전 근사에서 VGS − Vth에 매우 크게 의존하기 때문에, Vth가 조금만 올라가도 drain current가 눈에 띄게 줄어들 수 있습니다. UC Davis 자료도 MOS 동작을 설명할 때 전류가 VGS와 VT의 차이에 크게 좌우된다고 정리하고 있습니다.

그래서 바디 효과는 단순히 “문턱전압 숫자가 조금 바뀌는 현상”이 아니라, 실제 회로에서는 속도, 스윙, 전류 구동력, 동작 마진까지 건드리는 중요한 요소가 됩니다.

source follower에서 특히 자주 보이는 이유

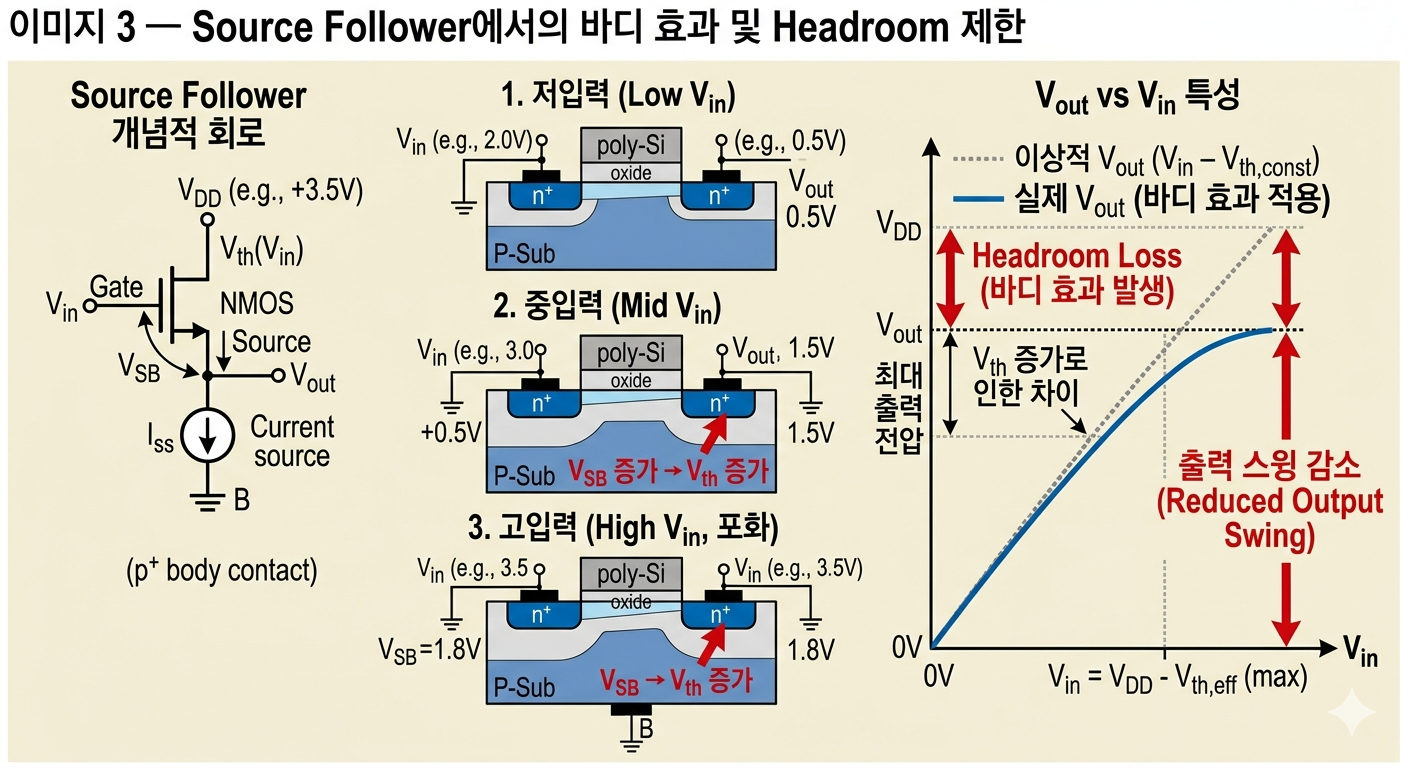

바디 효과를 가장 직관적으로 체감하기 좋은 회로 중 하나가 source follower입니다.

source follower에서는 입력이 올라가면 source 출력도 같이 올라가야 합니다.

그런데 source가 올라가는 순간 body가 고정되어 있다면 VSB도 함께 커집니다. 그러면 Vth가 올라가고, 결과적으로 source가 입력을 끝까지 잘 따라가지 못하게 됩니다.

즉, source follower는 이름 그대로 “따라가는” 회로이지만, 실제로는 body effect 때문에 완벽하게 따라가지 못하고 헤드룸을 잃게 되는 것입니다. U of Toronto 자료도 Vt 증가가 특히 source-follower 증폭기에서 available signal swing을 줄인다고 설명합니다.

이 부분이 중요한 이유는 회로를 처음 배울 때는

“출력은 입력에서 VGS 하나 빠진 정도겠지”

라고 단순하게 생각하기 쉬운데, 실제로는 그 VGS 자체가 body effect 때문에 다시 변할 수 있기 때문입니다.

직렬로 쌓인 MOS 구조에서도 왜 중요할까

CMOS 회로나 pass device, stacked transistor 구조를 볼 때도 바디 효과는 자주 등장합니다.

예를 들어 직렬로 연결된 NMOS 두 개가 있고, 아래쪽 transistor가 어느 정도 켜져 있어서 위쪽 transistor의 source 전압이 떠오른다고 생각해보겠습니다. 그러면 위쪽 transistor는 body가 보통 GND에 묶여 있으므로 VSB가 양수가 되고, 그만큼 Vth가 증가합니다.

UC Davis 강의 자료도 source 전압 상승이 VT 증가로 이어지며, 이는 series stacks of devices에서 중요한 설계 이슈라고 짚습니다.

결국 위쪽 transistor는 아래쪽 transistor보다 덜 잘 켜집니다.

그래서 단순히 “gate에 같은 전압을 걸었으니 두 소자가 비슷하게 켜질 것”이라고 보면 실제 회로와 어긋날 수 있습니다.

이 차이는 레벨 시프터, pass transistor, analog bias 회로, 픽셀 회로, source follower 기반 구조 같은 곳에서 꽤 실질적인 오차로 이어질 수 있습니다. U of Toronto 자료 역시 bulk가 source에 대해 또 하나의 gate처럼 작용한다고 설명합니다.

소신호 관점에서는 어떻게 보일까

큰 신호에서는 “Vth가 변한다”로 이해하면 충분하지만, 소신호 해석에서는 바디 효과가 추가 transconductance처럼 보입니다.

대표적으로 다음과 같이 씁니다.

gmb = χgm

여기서 χ는 body effect에 의해 생기는 비율 계수이고, U of Toronto 자료는 χ의 전형적인 값을 대략 0.1~0.3 정도로 제시합니다. 즉, body는 완전히 무시할 수 있는 단자가 아니라, 경우에 따라 gate 못지않게 drain current 변화에 영향을 주는 보조 제어 단자처럼 작동합니다.

실무에서는 이 때문에 소신호 이득, 출력 저항, follower 특성, 공통게이트/공통드레인 해석 결과가 이상적인 3단자 MOSFET 직관과 조금 달라질 수 있습니다.

PMOS에서는 반대로 생각해야 할까

PMOS도 본질은 같습니다.

핵심은 source와 body 사이 전압 차이가 생기면 |Vth|가 변한다는 점입니다.

부호 체계는 NMOS와 다르게 보일 수 있지만, 설계 관점에서는 보통 이렇게 이해하면 편합니다.

source와 body가 멀어질수록 transistor를 켜는 기준 전압이 더 불리해진다.

UC Davis 자료도 NMOS와 PMOS에서 substrate bias 계수와 VSB 부호가 다르게 나타난다는 점을 표로 비교해 보여줍니다.

그래서 설계할 때 무엇을 조심해야 할까

바디 효과는 개념 자체는 간단하지만, 실제 회로에서 놓치기 쉬운 이유가 있습니다.

회로도만 볼 때는 gate 전압이 가장 눈에 잘 들어오지만, 실제 동작에서는 source 전압이 움직이면서 VSB가 함께 변하기 때문입니다.

그래서 아래 상황에서는 특히 바디 효과를 의식하는 편이 좋습니다.

- source 전압이 크게 흔들리는 source follower

- 직렬로 쌓인 MOS 구조

- pass transistor

- 아날로그 바이어스 회로

- body가 source에 직접 묶이지 않는 집적회로 환경

결국 중요한 것은 Vth를 절대 고정 상수처럼만 보지 않는 것입니다.

source와 body 사이 관계가 달라지면, 문턱전압도 따라 움직일 수 있습니다.

정리하며

바디 효과는 “body 전압이 문턱전압에 영향을 주는 현상”이라는 한 줄로 설명할 수 있습니다.

하지만 실제 의미는 그보다 조금 더 큽니다.

이 현상 때문에 같은 gate 전압을 걸어도 transistor가 어제와 똑같이 켜지지 않을 수 있고, source가 올라갈수록 오히려 더 안 켜지는 것처럼 보일 수도 있습니다.

특히 NMOS에서는 VSB가 커질수록 Vth가 증가하고, 그 결과 VGS − Vth가 줄어들어 전류가 감소합니다. 이것이 source follower의 출력 제한, stacked MOS의 구동력 저하, pass 동작 열화 같은 회로 현상으로 이어집니다.

즉, 바디 효과는 문턱전압을 “조금 수정하는 보정항”이 아니라,

회로 해석에서 왜 예상보다 덜 켜지고, 덜 따라가고, 덜 흐르는지를 설명해주는 꽤 본질적인 개념이라고 볼 수 있습니다.

댓글