안녕하세요.

“기억하고자 하는 모든 것”을 담아내는 리멤버미입니다.

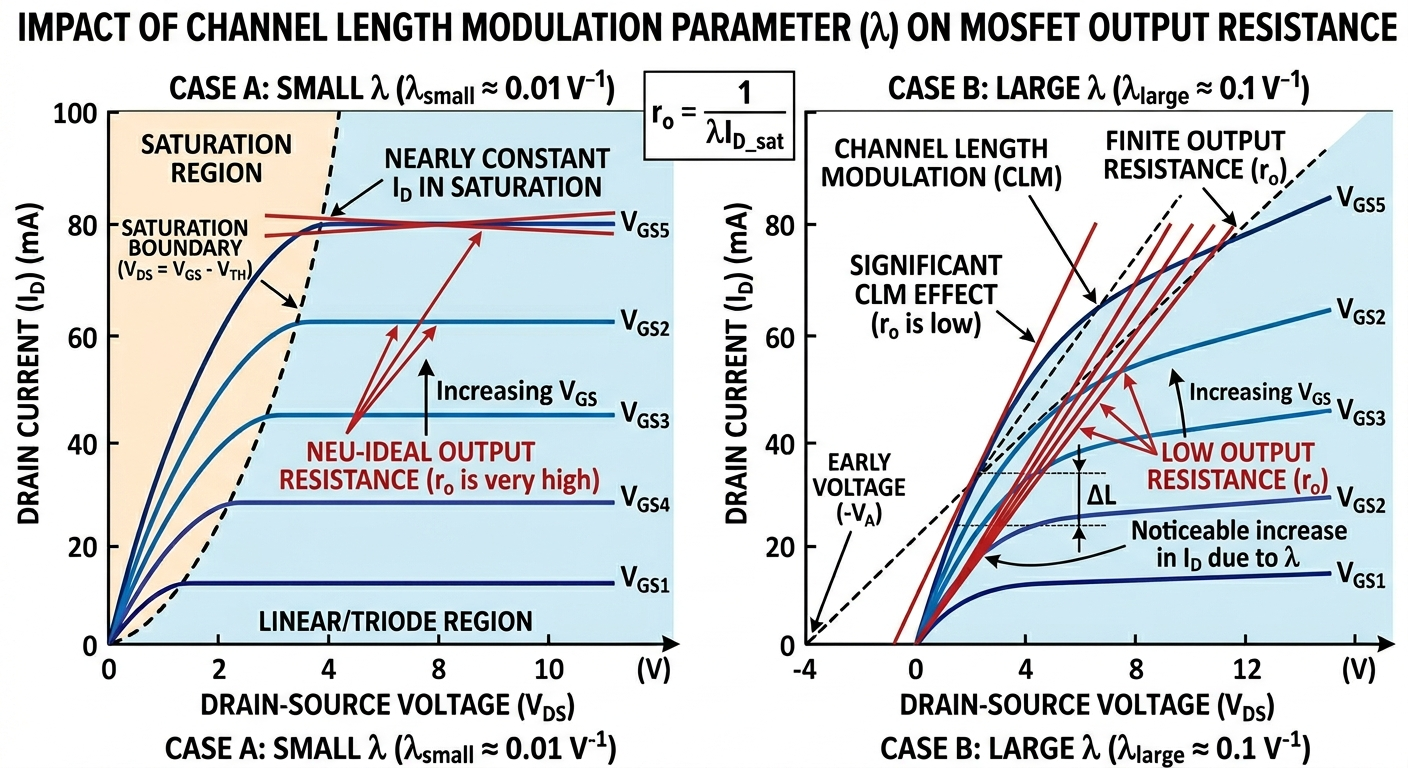

MOSFET을 공부하다 보면 포화영역(saturation region)에 들어가면 드레인 전류가 거의 일정하다고 배웁니다.

그래서 처음에는 이렇게 생각하기 쉽습니다.

“VDS가 충분히 커져서 포화영역에 들어가면, 그 뒤로는 ID가 더 이상 안 변해야 하는 것 아닌가?”

“그런데 실제 ID-VDS 그래프를 보면 포화영역에서도 전류가 완전히 평평하지 않고 조금씩 올라가는데, 그 이유는 뭘까?”

핵심만 먼저 말하면,

채널 길이 변조(Channel Length Modulation, CLM)는 드레인 전압이 더 커질수록 채널의 유효 길이(effective channel length)가 짧아져서, 포화영역에서도 드레인 전류가 조금씩 증가하는 현상입니다.

즉, 이상적인 MOSFET이라면 포화영역 전류가 완전히 일정해야 하지만, 실제 소자에서는 채널 길이가 고정된 값처럼 유지되지 않기 때문에 출력 특성에 기울기가 생깁니다.

먼저, 이상적인 포화영역은 어떤 모습인가

기본적인 long-channel MOSFET 모델에서는

VDS가 충분히 커져서

VDS ≥ VGS - VT

조건이 되면 채널의 드레인 쪽 끝이 pinch-off 상태에 도달한다고 설명합니다.

이때부터는 드레인 전류가 거의 VDS와 무관한 일정값처럼 보이며, 그래서 포화영역을 “전류원처럼 동작하는 구간”이라고 이해합니다. 하지만 실제 측정 곡선을 보면, 포화영역의 ID-VDS 특성이 완전히 수평이 아니라 약간 우상향합니다.

즉, 드레인 전압을 더 올리면 전류가 아주 조금씩 더 증가합니다.

바로 이 “완전한 평탄함이 깨지는 이유”를 설명하는 대표적인 개념이 채널 길이 변조입니다.

왜 채널 길이가 줄어드는가

핵심은 pinch-off가 생긴 뒤의 드레인 쪽 영역입니다.

VDS가 커져서 드레인 쪽 채널 전하가 0에 가까워지면, 채널 끝은 드레인 바로 직전에서 끊긴 것처럼 보입니다.

그런데 여기서 VDS를 더 키우면, pinch-off 지점이 드레인 쪽에 그대로 있는 것이 아니라 소스 방향으로 조금 이동하게 됩니다.

그러면 실제로 전류가 흐르는 채널의 길이는 처음보다 더 짧아집니다.

원래 전류식에서 채널 길이 L은 분모에 들어갑니다.

따라서 유효 채널 길이 Leff가 짧아지면 같은 VGS에서도 전류가 더 커지게 됩니다.

즉, 포화영역이라고 해서 전류가 완전히 고정되는 것이 아니라, VDS 증가 → 유효 채널 길이 감소 → ID 증가라는 연결이 생깁니다.

식으로 보면 더 직관적이다

1차 모델에서는 포화영역 전류를 보통 이렇게 씁니다.

ID,sat ≈ (1/2)·μn·Cox·(W/L)·(VGS - VT)²·(1 + λVDS)

여기서 λ(lambda)는 채널 길이 변조 계수입니다.

이 항이 없으면 포화영역 전류는 VDS와 무관한 상수처럼 보이지만,

(1 + λVDS) 항이 들어가면 VDS가 증가할수록 ID도 함께 증가하게 됩니다.

이 식이 말해주는 물리적 의미는 단순합니다.

“포화영역에서도 드레인 전압이 커질수록 채널 길이가 약간 줄어드는 효과를, λ라는 파라미터로 묶어서 표현한다”는 것입니다.

그래서 λ가 클수록 포화곡선의 기울기가 더 커지고, 전류원 특성은 더 나빠집니다.

출력 저항 ro와는 어떤 관계가 있을까

채널 길이 변조가 생기면 포화영역의 ID-VDS 곡선에 기울기가 생깁니다.

이 기울기를 small-signal 관점에서는 출력 컨덕턴스 gds로 보고,

gds = dID/dVDS

로 정의합니다.

그리고 출력 저항은 대략

ro = 1/gds

로 봅니다.

즉, CLM이 크다는 말은 gds가 커진다는 뜻이고, 결국 ro는 작아진다는 뜻입니다.

1차 근사에서는 위 식으로부터 흔히

ro ≈ 1 / (λID)

처럼 정리해서 이해합니다.

그래서 λ가 큰 소자일수록 포화영역에서 이상적인 전류원과 멀어지고, current mirror나 증폭기에서 gain이 떨어지는 방향으로 작용합니다. Berkeley 자료도 출력 컨덕턴스 gds가 커지면 intrinsic gain이 작아진다고 설명합니다.

왜 짧은 채널에서 더 심해지는가

채널 길이 변조는 특히 short-channel 소자에서 더 중요해집니다.

채널이 원래부터 짧으면, 드레인 전압 변화에 의해 줄어드는 유효 길이의 비율이 상대적으로 더 커지기 때문입니다.

아주 쉽게 말하면, 원래 길이가 긴 채널에서 0.02 μm 줄어드는 것과, 원래 길이가 매우 짧은 채널에서 0.02 μm 줄어드는 것은 영향이 다릅니다.

짧은 채널일수록 같은 절대 변화가 더 큰 비율 변화가 되고, 그만큼 전류 증가와 출력 특성 기울기가 더 눈에 띄게 됩니다.

MIT 자료와 Berkeley 자료 모두 짧은 채널일수록 포화 특성이 덜 이상적이고 출력 컨덕턴스가 커지기 쉬움을 보여줍니다.

Early effect와 비슷하다고 보면 이해가 쉽다

BJT에서 collector-emitter 전압이 증가할수록 base 폭이 줄어 전류가 변하는 현상을 Early effect라고 부릅니다.

MOSFET의 채널 길이 변조도 개념적으로는 꽤 비슷합니다.

둘 다 “전압이 커질수록 전류가 흐르는 유효 길이 또는 유효 영역이 줄어들어, 이상적인 전류원 특성이 깨진다”는 공통점을 갖습니다. 그래서 어떤 교재에서는 CLM을 MOSFET의 Early effect에 대응되는 현상처럼 설명하기도 합니다.

회로에서는 어떤 문제가 생길까

채널 길이 변조는 단순히 그래프 모양만 조금 바꾸는 현상이 아닙니다.

실제 회로에서는 꽤 중요한 차이를 만듭니다.

아날로그 회로에서는 포화영역의 MOSFET을 이상적인 전류원처럼 쓰고 싶을 때 ro가 작아져 gain이 감소할 수 있습니다.

current mirror의 정확도도 떨어질 수 있고, 증폭기 출력 저항이 낮아져 원하는 증폭도를 얻기 어려워질 수 있습니다.

디지털 회로에서도 완전히 무관한 것은 아닙니다.

인버터 전이 특성, 노이즈 마진, 단락 전류 구간, 지연 특성 등을 더 현실적으로 이해하려면 포화영역 전류가 완전한 상수가 아니라는 점을 알아야 합니다.

즉, CLM은 “아날로그에서만 중요하다”기보다는, MOSFET을 이상 소자가 아닌 실제 소자로 이해할 때 반드시 등장하는 보정 개념에 가깝습니다.

설계자는 이것을 어떻게 다룰까

채널 길이 변조를 완전히 없애기는 어렵지만, 줄이는 방향은 분명합니다.

가장 기본적으로는 채널 길이를 너무 공격적으로 줄이지 않는 것이 도움이 됩니다.

Berkeley 자료도 작은 gds를 얻기 위해서는 더 큰 L이 유리하다고 설명합니다.

회로 차원에서는 cascode 구조를 써서 소자의 VDS 변화를 줄이는 방식이 자주 사용됩니다.

왜냐하면 CLM은 결국 드레인 전압 변화가 유효 채널 길이에 영향을 주는 현상이므로, 소자에 걸리는 VDS를 덜 흔들리게 만들면 그 영향도 줄일 수 있기 때문입니다.

그래서 아날로그 설계에서는 ro를 키우고 gain을 확보하기 위해 cascode가 매우 자주 등장합니다.

마무리하며

채널 길이 변조(Channel Length Modulation)는 이름만 보면 단순히 “길이가 조금 바뀌는 효과”처럼 들릴 수 있습니다.

하지만 실제로는 포화영역 전류가 왜 완전히 일정하지 않은지, 그리고 왜 실제 MOSFET이 이상적인 전류원처럼 동작하지 않는지를 설명하는 아주 중요한 개념입니다.

한 줄로 다시 정리하면 이렇습니다.

채널 길이 변조란, 드레인 전압이 증가할수록 pinch-off 지점이 이동해 유효 채널 길이가 짧아지고, 그 결과 포화영역에서도 드레인 전류가 조금씩 증가하는 현상입니다.

앞으로 MOSFET의 ID-VDS 곡선을 볼 때 포화영역이 완전히 수평이 아니라면, 그건 측정이 이상한 것이 아니라 실제 소자의 물리를 잘 보여주는 결과라고 생각하면 됩니다.

댓글